- Los transistores forksheet introducen una pared dieléctrica que permite acercar más los dispositivos n y p, mejorando densidad, rendimiento y eficiencia frente a los nanosheet GAA.

- Samsung planea usar forksheet en su hoja de ruta hacia el nodo de 1 nm, mientras imec impulsa variantes como el outer wall forksheet para facilitar la fabricación hasta el nodo A10.

- La metrología avanzada, incluida la elipsometría de matriz de Mueller, es clave para detectar asimetrías y defectos críticos en estructuras forksheet cada vez más complejas.

- El forksheet se posiciona como paso intermedio estratégico hacia los futuros CFET, compartiendo procesos y conocimientos que facilitarán la transición a arquitecturas verticales apiladas.

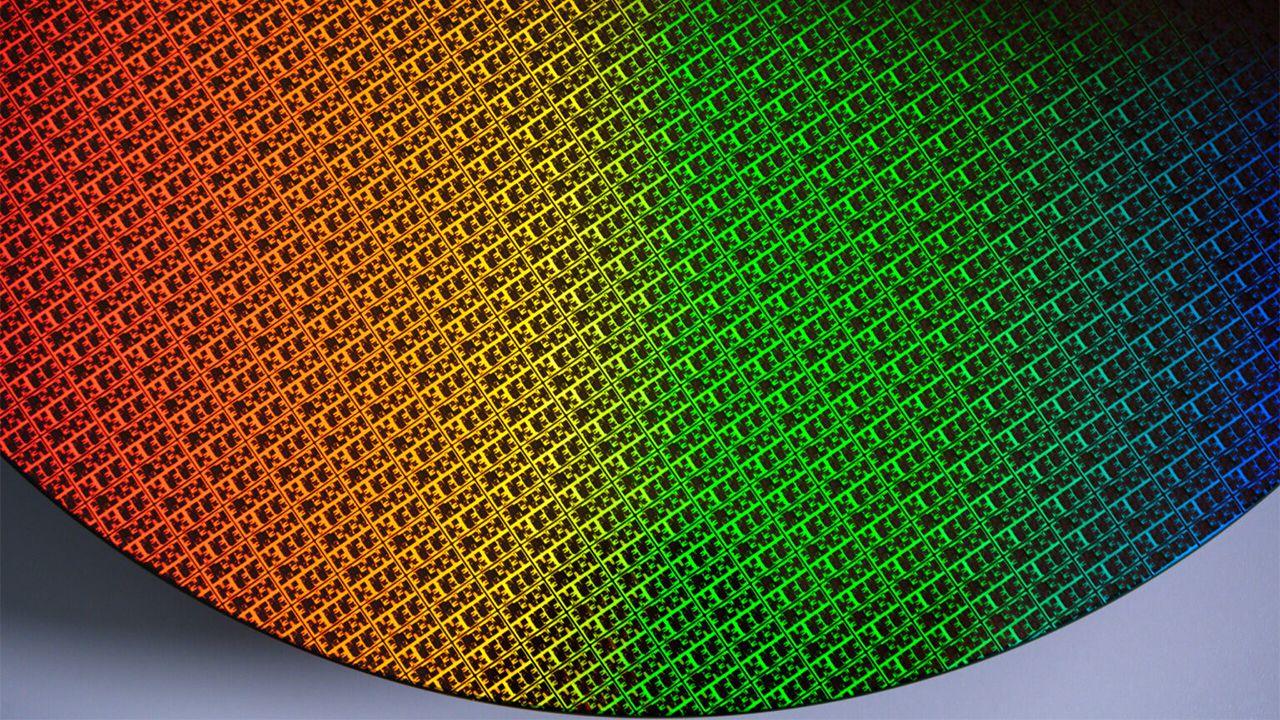

La industria de los semiconductores está viviendo un momento clave: los transistores forksheet se han colado en todas las hojas de ruta de los fabricantes punteros como la siguiente gran vuelta de tuerca para seguir escalando más allá de los nanosheet GAA tradicionales. Y no es casualidad: cada nodo nuevo es más caro, más complejo y más delicado, así que cualquier arquitectura que exprima más densidad, rendimiento y eficiencia sin reventar los costes se convierte automáticamente en protagonista.

Dentro de este panorama, Samsung, Intel, TSMC e imec se están moviendo a toda velocidad para definir cómo serán los nodos de 2 nm, 1 nm y las futuras generaciones angstrom (A14, A10, A7, etc.). En ese camino, el forksheet está llamado a ser un “paso intermedio inteligente” entre los actuales nanosheet GAA y los futuros CFET (Complementary FET), que llegarán cuando la integración vertical de dispositivos n y p uno encima de otro sea una realidad industrial y no solo de laboratorio.

Qué es un transistor forksheet y por qué importa tanto

El transistor forksheet es una evolución directa del transistor nanosheet GAA, pensada para exprimir al máximo la densidad de lógica y SRAM sin tener que rediseñar todo el flujo de fabricación desde cero. La clave está en introducir una pared dieléctrica estratégica que permita colocar transistores nMOS y pMOS mucho más cerca unos de otros sin disparar la capacitancia parásita.

En los nanosheet GAA convencionales, la limitación no viene tanto del canal en sí como de la distancia entre los dispositivos complementarios que forman una puerta lógica CMOS. Si se juntan demasiado, la capacitancia entre áreas n y p se dispara, se degrada el rendimiento, sube el consumo y la señal se contamina. Esa distancia mínima se estaba convirtiendo en un auténtico cuello de botella para seguir reduciendo el tamaño de las celdas estándar.

Imec, que lleva años tirando del carro en investigación de dispositivos avanzados, se puso a estudiar dónde empezaba a “romperse” la escalabilidad de los nanosheet. El resultado de esos estudios fue la idea del forksheet: en lugar de dejar “a la intemperie” el espacio entre los transistores complementarios, se introduce una pared aislante que separa físicamente zonas n y p o, según la variante, dispositivos del mismo tipo.

En su concepción original, el forksheet colocaba una pared dieléctrica interna entre el nMOS y el pMOS dentro de la misma celda estándar. Esta pared permite acercar aún más los dos transistores sin incrementar tanto la capacitancia, porque actúa como barrera eléctrica entre las puertas y las regiones activas. Así, el diseñador se ve con dos opciones: reducir el área de la celda para meter más lógica por milímetro cuadrado o aprovechar el espacio “extra” para ensanchar los nanosheets y ganar rendimiento.

Los números que maneja la industria no son menores: según simulaciones, frente a un nanosheet GAA clásico, un diseño forksheet puede lograr hasta un 10 % más de rendimiento, una mejora de en torno al 24 % en eficiencia energética y una reducción de área de la celda cercana al 20 %. Todo ello, manteniendo buena parte de los pasos de proceso ya dominados para los nanosheet.

Del FinFET al GAA y del GAA al forksheet: el siguiente escalón

Para entender dónde encaja el forksheet, hay que mirar un momento hacia atrás. Cuando los FinFET llegaron al mercado, resolvieron el problema de control de canal que sufrían los transistores planos a medida que el nodo se iba encogiendo. El “fin” o aleta elevaba el canal en 3D y la puerta abrazaba tres lados, mejorando el control electrostático y reduciendo fugas.

El siguiente salto ha sido el gate-all-around (GAA), donde el canal ya no es una aleta sino varias láminas horizontales de silicio apiladas, rodeadas completamente por la puerta. Esto vuelve a fortalecer el control del canal y permite escalar a 3 nm, 2 nm y un poco más allá. Intel, TSMC y Samsung están en plena transición a esta arquitectura con sus nodos Intel 18A, TSMC N2 y Samsung SF3E, entre otros.

Sin embargo, incluso el GAA con nanosheets tiene fecha de caducidad. La gran aspiración de la industria lógica es el CFET, donde los transistores n y p se apilan verticalmente uno encima del otro, de forma que, a nivel de planta, ocupan la huella de un solo dispositivo. Eso podría prácticamente partir por la mitad el área de ciertas celdas críticas y proporcionar mejoras brutales de densidad y PPA (power, performance, area).

El problema es que el CFET es una auténtica pesadilla de integración. Requiere un control material y un alineamiento extremo entre dispositivos apilados, además de una coreografía de procesos muy delicada para no arruinar los transistores de abajo mientras se fabrica lo de arriba. De ahí que imec y otros actores consideren el forksheet como una parada intermedia razonable: reutiliza la mayor parte del flujo GAA, añade una pared dieléctrica y mejora la densidad sin dar todavía el salto a la apilación vertical completa.

Desde la óptica temporal, imec sitúa al forksheet como protagonista hacia finales de esta década, con vistas a producción alrededor de 2028, mientras que el CFET de alta gama se perfilaría más bien para principios-mediados de los años 30, con madurez de producción industrial aproximada hacia 2032 según sus estimaciones.

La visión de Samsung: forksheet para llegar a 1 nm

Samsung Foundry no se limita ya a competir nodo a nodo con TSMC o a perseguir el calendario de Intel; los coreanos han fijado claramente la vista en el nodo de 1 nm para alrededor de 2031, y allí el forksheet es una pieza central de su estrategia. La compañía quiere jugar fuerte en densidad, eficiencia y prestaciones, aunque el liderazgo en volumen lo siga teniendo TSMC.

En este plan, Samsung plantea usar transistores con anchuras de canal cercanas a 1 nm, que equivale a unos cinco átomos. No se trata solo de una reducción incremental respecto a los 2 nm, sino de una auténtica frontera física actual en lo que respecta al control del canal, el manejo de materiales y la variabilidad estadística de dispositivo a dispositivo.

El enfoque forksheet de Samsung busca reducir al mínimo el espacio entre transistores aprovechando los límites de lo que permiten los escáneres litográficos actuales. Entre dispositivos se introduce una “pared” aislante que contiene la interacción eléctrica entre ellos, y con ello se empuja aún más la densidad por unidad de área. Menos separación física significa más transistores en el mismo espacio, pero también más exigencia en el control de fugas y acoplamientos, por eso la pared dieléctrica es crítica.

Hasta ahora, el salto de FinFET a GAA ya había permitido una mejora notable de eficiencia energética, ya que el canal rodeado en 4 lados reduce fugas respecto a la puerta de 3 lados de los FinFET. El forksheet añade una optimización adicional atacando uno de los grandes cuellos de botella: la distancia física entre dispositivos n y p dentro de la celda. Para escalar más allá de los 2 nm sin perder el norte en consumo ni deteriorar el rendimiento, este tipo de soluciones agresivas se vuelven imprescindibles.

En el contexto de mercado, Samsung sigue siendo el segundo gran actor en fundición por volumen, pero TSMC se mueve en otra liga con más del 70 % de cuota mundial. Aun así, los coreanos han sabido jugar la carta de la innovación puntual: fueron los primeros en introducir EUV en su nodo de 7 nm y también en poner en producción GAA en 3 nm. Esto no les ha dado el liderazgo en ingresos, pero sí una presencia constante en la conversación tecnológica.

El nodo de 1 nm con forksheet hay que verlo, por ahora, como una señal de territorio y ambición tecnológica más que como algo que vaya a inundar el mercado de inmediato. El gran reto será transformar esa ventaja teórica de densidad y PPA en producción real con yields razonables y costes asumibles. Ahí es donde históricamente se decide quién gana de verdad: no en la presentación en conferencias, sino en la fábrica.

Inner wall y outer wall: la evolución del diseño forksheet

Cuando imec presentó el concepto forksheet en 2017, la arquitectura original se basaba en una “pared interior” (inner wall) situada entre los dispositivos nMOS y pMOS dentro de la celda estándar. El muro aislante se introducía temprano en el flujo, antes del patrón de puerta, y a partir de ahí debía sobrevivir a un sinfín de pasos de proceso: grabados selectivos, depósitos de diferentes dieléctricos, tratamientos térmicos, etc.

Esta aproximación presentaba varias dificultades significativas. La anchura de esa pared tenía que ser extremadamente pequeña, del orden de 8 a 10 nm, si se quería mantener una altura de celda en torno a 90 nm. Con un muro tan fino expuesto a tantos pasos posteriores, cualquier ligera sobre-etch o ataque químico podía erosionarlo de forma incontrolable. Eso imponía requisitos muy estrictos sobre el material dieléctrico y las tolerancias del proceso.

Además, en muchos diseños lógicos las puertas de los transistores n y p comparten parte del trazado. Al interponer una barrera rígida entre ellos, esa conexión se complica: o bien la puerta tiene que “saltar” por encima de la pared, lo que añade capacitancia parásita no deseada, o se necesitan soluciones de enrutado más raras que acaban penalizando rendimiento y área.

Otro punto delicado del inner wall forksheet era el control de canal. La geometría de la puerta en la implementación inicial solo abrazaba realmente tres lados del canal, por lo que el control electrostático no era tan bueno como el de un GAA de libros de texto. A medida que las longitudes de canal siguen reduciéndose, esa pérdida relativa de control se vuelve cada vez más problemática.

Ante estas limitaciones, imec ha dado un giro de tuerca con una nueva variante llamada “outer wall forksheet”. En esta versión, la pared aislante pasa a situarse en el borde de la celda estándar, separando dispositivos del mismo tipo que pertenecen a celdas adyacentes, en lugar de intercalar la barrera dentro de la propia celda entre el nMOS y el pMOS. Esto cambia bastante el enfoque de integración.

Al redactar la pared hacia el exterior, se puede aumentar su anchura hasta unos 15 nm sin penalizar la altura total de la celda. Eso permite construirla con materiales y herramientas bien conocidos, como el dióxido de silicio, y, sobre todo, introducirla más tarde en la secuencia de fabricación, una vez completados pasos críticos como la formación de source/drain o la liberación de los nanosheets. Al llegar más tarde al flujo, la pared se ve expuesta a menos procesos agresivos y resulta más fácil mantener su integridad.

Ventajas del outer wall forksheet: mejor control y más facilidad de fabricación

La reubicación de la pared en el outer wall forksheet no solo favorece la manufacturabilidad, también simplifica la integración de la puerta de los transistores. Ahora la puerta puede extenderse de forma continua sobre los dispositivos n y p sin tener que cruzar una barrera en mitad de la celda, lo que reduce la complejidad de enrutado y evita añadir capacitancia parásita innecesaria.

Otro truco interesante del outer wall forksheet consiste en recortar ligeramente la pared al final del proceso. Si en los pasos finales se comen unos 5 nm de ese muro, la puerta puede envolver una porción mayor del canal, recuperando y hasta mejorando el control electrostático respecto a la variante previa. Las simulaciones que ha presentado imec apuntan a un incremento de alrededor del 25 % en la corriente de conducción gracias a esa mejora en el acoplamiento puerta-canal.

El nuevo diseño también resuelve un problema clásico de los nanosheet y de la primera hornada de forksheet: la continuidad del esfuerzo mecánico (strain) en el canal. Durante el proceso, una máscara protectora cubre la zona donde más tarde se formará la pared exterior, de forma que el silicio bajo esa máscara permanece como un “bloque” cristalino continuo. Eso permite que los materiales de source/drain que inducen tensión —por ejemplo, silicio-germanio para pMOS— transmitan el strain de manera más eficiente hacia el canal.

En las arquitecturas anteriores, con interrupciones verticales y discontinuidades, ese esfuerzo mecánico se veía mermado por desalineaciones y defectos. El resultado era una menor movilidad de portadores y, por tanto, menos corriente para el mismo voltaje. El outer wall forksheet evita en buena parte esos problemas, permitiendo aplicar strain de forma más uniforme y sistemática.

Las simulaciones en memorias SRAM y en osciladores confirman que en un nodo A10 (entorno a 1 nm / 10 angstroms), la nueva disposición puede lograr una reducción de área de celda de alrededor del 22 % respecto a diseños A14 basados en nanosheet, aprovechando un gate pitch más ajustado y el empaquetado más denso de dispositivos del mismo tipo. En circuitos osciladores, cuando se aplica strain “a tope”, el rendimiento del outer wall forksheet iguala o supera al de diseños A14 y 2 nm equivalentes; sin strain, la corriente de conducción cae aproximadamente un 33 %, lo que subraya lo crítico que es este factor.

Más allá de las cifras concretas, la gran baza del outer wall forksheet es que recicla buena parte del know-how de nanosheet: usa materiales ya conocidos, equipos que existen en las fábricas actuales y secuencias de proceso que no exigen reconstruir la planta entera. Eso reduce riesgo, costes y tiempo de maduración frente a alternativas más disruptivas.

Retos de metrología y defectos en estructuras forksheet

Mientras las estructuras de los transistores se vuelven más pequeñas y enrevesadas, la detección de defectos se convierte en un quebradero de cabeza cada vez mayor. En CMOS de última generación, el desafío ya no es solo “hacer el transistor”, sino ser capaz de ver y medir con precisión defectos estructurales minúsculos que, sin embargo, tienen un impacto enorme en el comportamiento eléctrico.

En el caso de los forksheet FET, aunque se gane densidad, rendimiento y eficiencia teórica, el tamaño absoluto de los defectos típicos (rugosidad de línea, desviaciones de pitch, curvaturas, asimetrías del perfil, etc.) no disminuye en la misma proporción que las dimensiones nominales del dispositivo. Eso significa que cualquier pequeña anomalía ocupa, en términos relativos, una porción cada vez mayor del transistor, con efectos más acusados.

En este contexto, las técnicas de metrología clásicas se quedan cortas para caracterizar adecuadamente estas nuevas arquitecturas. Dentro del proyecto europeo IT2, la compañía Semilab y sus expertos en elipsometría espectroscópica han desarrollado métodos de elipsometría generalizada y, en particular, han explorado el uso de la matriz de Mueller (Mueller Matrix Ellipsometry) para detectar asimetrías estructurales en arrays de forksheet FET.

La idea pasa por simular mediciones de matriz de Mueller bajo diferentes grados y direcciones de asimetrías en el perfil de los forksheet: variaciones sutiles en la inclinación de paredes, diferencias entre ramas, pequeños doblados o desalineaciones. A partir de estas simulaciones se cuantifica hasta qué punto las respuestas ópticas asociadas a cada tipo de defecto se pueden distinguir unas de otras y se calcula la correlación entre parámetros de asimetría.

Un factor crítico en este tipo de medición óptica avanzada es la alineación precisa de la muestra. Un ligero error en el posicionamiento puede enmascarar o imitar ciertas asimetrías, así que parte del trabajo se centra en entender cómo afecta la incertidumbre de alineación a las medidas y en diseñar métodos para filtrarla o compensarla.

Este tipo de desarrollos son fundamentales para la industria europea, que busca reforzar su papel como actor tecnológico relevante en semiconductores. Más allá de fabricar o no los nodos más avanzados, proyectos como este aportan herramientas de caracterización y conocimiento de procesos que permiten afinar la fabricación y mejorar el rendimiento de dispositivos cada vez más complejos, entre ellos los forksheet.

Forksheet como puente hacia los CFET y el futuro más allá de 2 nm

Los principales fabricantes de lógica coinciden en que el GAA basado en nanosheet no podrá estirarse indefinidamente más allá de unas pocas generaciones. A medida que se bajan los nodos —2 nm, A14, A10 y lo que venga después— se agotan las palancas de escalado puramente geométrico y se necesitan cambios más radicales de arquitectura; demandas como la computación cuántica son un ejemplo de por qué se buscan rutas nuevas de densidad y rendimiento.

En ese escenario, el CFET aparece como la “arquitectura CMOS definitiva” a largo plazo, según palabras de expertos de imec. Al apilar verticalmente un transistor n y uno p, se consigue reducir de forma drástica el área de ciertos bloques lógicos y de memoria, aumentando la densidad sin necesidad de seguir exprimiendo el pitch lateral hasta límites impracticables.

Pero, como ya se ha comentado, la integración de CFET es enormemente compleja. Hay que controlar interfaces, tensiones, alineamientos y pasos de proceso que se encadenan con un nivel de precisión muy por encima de lo que hoy es rutinario. Por eso, la industria necesita una transición progresiva que le permita aprender, en producción, a manejar estructuras híbridas y paredes dieléctricas críticas sin jugárselo todo a una tecnología todavía verde.

Los forksheet, y en particular la variante outer wall, se encajan justo en este hueco. Muchas de las lecciones de fabricación que se obtengan al producir forksheet a gran volumen serán reaprovechables para los CFET: desde el manejo de paredes aislantes finas, hasta el control del strain, pasando por la integración de puertas compartidas y la administración de defectos en entornos de altísima densidad.

Imec sitúa al outer wall forksheet como arquitectura clave para extender la era nanosheet hasta el nodo A10, mientras el CFET va ganando madurez para introducirse en masa más adelante en la década de 2030. En la práctica, esto significa que durante varios nodos veremos convivir y solaparse arquitecturas: primeros forksheet en producción, CFET en líneas piloto, GAA “clásicos” todavía en volúmenes grandes para mercados que no necesiten lo último de lo último, etc.

También se está discutiendo qué tipo de transistores colocar a cada lado de la pared en los diferentes sabores de forksheet. La idea original ponía nMOS en un lado y pMOS en el otro, como en un CMOS clásico. Sin embargo, se barajan configuraciones donde se ponen dispositivos del mismo tipo a ambos lados para optimizar ciertas celdas o mejorar rutas críticas, según las necesidades del diseño y el tipo de circuito (lógica, SRAM, osciladores, etc.). A día de hoy, esa elección sigue siendo un campo abierto de investigación y optimización.

De cara a los próximos años, la apuesta del sector es clara: usar forksheet para mantener viva la escalada de densidad y prestaciones con una inversión incremental en proceso, y reservar el salto más dramático para el momento en que los CFET estén realmente listos y las herramientas de fabricación y metrología puedan soportarlo sin hundir los yields.

Todo este movimiento alrededor de los transistores forksheet deja entrever que, aunque la física ponga límites duros, todavía queda juego para seguir apretando los nodos por debajo de 2 nm. La combinación de paredes dieléctricas bien diseñadas, control de strain, nuevos esquemas de metrología y una evolución gradual hacia arquitecturas verticales abre una ventana de oportunidades para que fabricantes como Samsung, junto con centros de referencia como imec, sigan marcando el ritmo tecnológico de la próxima década, siempre que consigan transformar estas ideas en líneas de producción estables y rentables.