- Transistor forksheet memperkenalkan dinding dielektrik yang membolehkan peranti nyp diletakkan lebih dekat antara satu sama lain, meningkatkan ketumpatan, prestasi dan kecekapan berbanding GAA nanosheet.

- Samsung merancang untuk menggunakan teknologi forksheet dalam pelan hala tujunya ke nod 1nm, manakala imec sedang memperkenalkan varian seperti forksheet dinding luar untuk memudahkan pembuatan sehingga nod A10.

- Metrologi lanjutan, termasuk elipsometri tatasusunan Mueller, adalah kunci untuk mengesan asimetri kritikal dan kecacatan dalam struktur forksheet yang semakin kompleks.

- Forksheet ini diletakkan sebagai langkah perantaraan strategik ke arah CFET masa hadapan, perkongsian proses dan pengetahuan yang akan memudahkan peralihan kepada seni bina menegak bertindan.

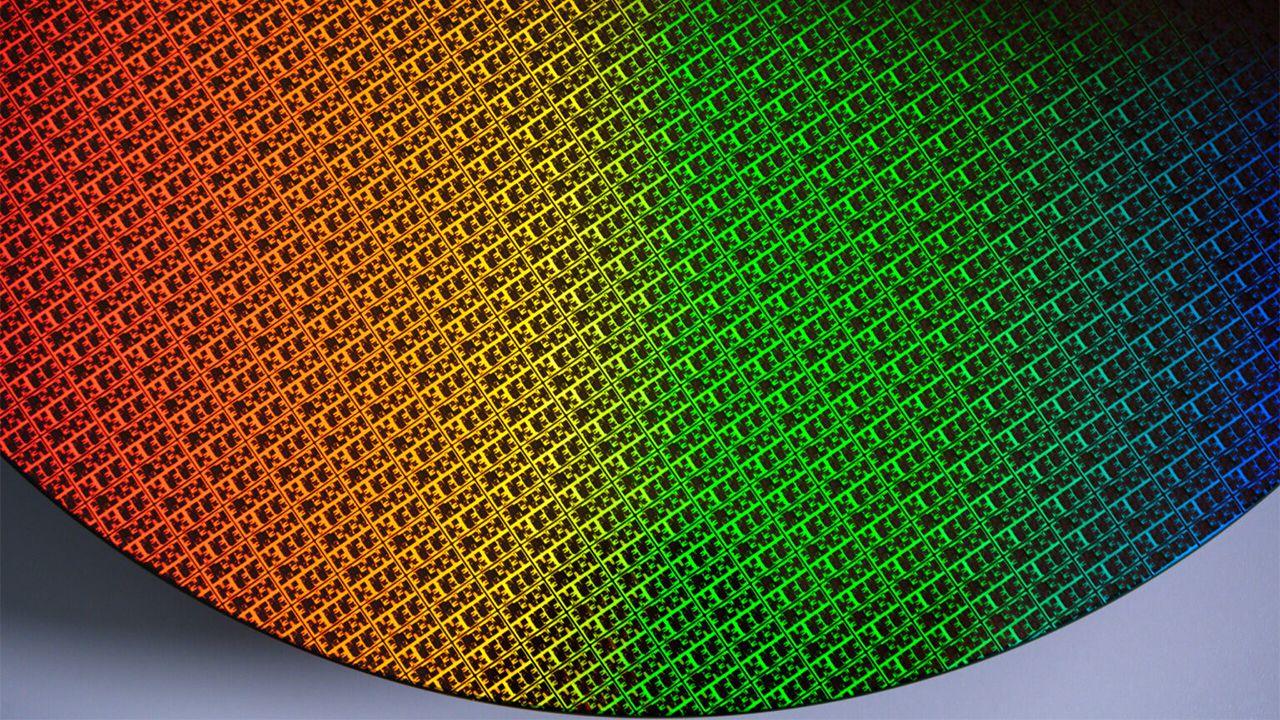

Industri semikonduktor sedang mengalami detik penting: Forksheet transistor telah menyelinap masuk ke dalam semua peta jalan Pengeluar terkemuka melihat ini sebagai langkah besar seterusnya untuk penskalaan melangkaui nanosheet GAA tradisional. Dan ia bukanlah satu kebetulan: setiap nod baharu lebih mahal, lebih kompleks dan lebih halus, jadi sebarang seni bina yang memaksimumkan ketumpatan, prestasi dan kecekapan tanpa kos yang melambung tinggi secara automatik menjadi pemain utama.

Dalam konteks ini, Samsung, Intel, TSMC dan imec bergerak pada kelajuan penuh untuk menentukan bagaimana nod generasi 2 nm, 1 nm dan generasi angstrom akan datang (A14, A10, A7, dsb.). Dalam proses ini, forksheet ditakdirkan untuk menjadi "langkah perantaraan pintar" antara GAA nanosheet semasa dan CFET (FET Pelengkap) akan datang, yang akan tiba apabila integrasi menegak peranti nanop yang disusun di atas satu sama lain menjadi realiti perindustrian dan bukan sekadar latihan makmal.

Apakah forksheet transistor dan mengapa ia sangat penting?

Transistor forksheet merupakan evolusi langsung transistor nanosheet GAA.Direka untuk memaksimumkan ketumpatan logik dan SRAM tanpa memerlukan reka bentuk semula lengkap proses pembuatan, kuncinya terletak pada memperkenalkan dinding dielektrik strategik yang membolehkan transistor nMOS dan pMOS diletakkan lebih dekat antara satu sama lain tanpa mencetuskan kapasitans parasit.

Dalam nanosheet GAA konvensional, Batasan itu bukan sahaja datang daripada saluran itu sendiri tetapi juga daripada jarak antara peranti pelengkap. yang membentuk get logik CMOS. Jika ia diletakkan terlalu dekat antara satu sama lain, kapasitans antara kawasan N/P meningkat secara mendadak, menjejaskan prestasi, meningkatkan penggunaan kuasa dan mencemari isyarat. Jarak minimum ini menjadi kesesakan sebenar untuk mengurangkan lagi saiz sel standard.

Imec, yang telah menerajui penyelidikan peranti canggih selama bertahun-tahun, mula mengkaji di mana kebolehskalaan nanosheets mula "rosak". Hasil daripada kajian tersebut adalah idea forksheetDaripada membiarkan ruang antara transistor pelengkap "terdedah", dinding penebat diperkenalkan yang secara fizikal memisahkan zon peranti jenis yang sama, bergantung pada variannya.

Dalam konsep asalnya, Forksheet meletakkan dinding dielektrik dalaman antara nMOS dan pMOS dalam sel piawai yang sama. Dinding ini membolehkan kedua-dua transistor diletakkan lebih dekat antara satu sama lain tanpa meningkatkan kapasitans dengan ketara, kerana ia bertindak sebagai penghalang elektrik antara get dan kawasan aktif. Oleh itu, pereka bentuk menghadapi dua pilihan: mengurangkan kawasan sel agar sesuai dengan lebih banyak logik setiap milimeter persegi atau menggunakan ruang "tambahan" untuk meluaskan nanosheet dan mendapatkan prestasi.

Angka-angka yang ditangani oleh industri ini tidaklah kecil: Menurut simulasi, berbanding dengan nanosheet GAA klasikReka bentuk forksheet boleh mencapai prestasi sehingga 10% lebih tinggi, peningkatan sekitar 24% dalam kecekapan tenaga dan pengurangan luas sel hampir 20%. Semua ini sambil mengekalkan sebahagian besar langkah proses yang telah dikuasai untuk nanosheet.

Dari FinFET ke GAA dan dari GAA ke forksheet: langkah seterusnya

Untuk memahami di mana kedudukan forksheet, kita perlu melihat ke belakang seketika. Apabila FinFET dipasarkan, ia menyelesaikan masalah kawalan saluran. bahawa transistor satah terjejas apabila nod mengecut. "Sirip" atau sirip menaikkan saluran dalam 3D dan get merangkumi tiga sisi, meningkatkan kawalan elektrostatik dan mengurangkan kebocoran.

Lompatan seterusnya ialah pintu gerbang keliling (GAA), di mana Saluran itu bukan lagi sirip tetapi beberapa kepingan silikon mendatar yang disusundikelilingi sepenuhnya oleh pintu gerbang. Ini mengukuhkan lagi kawalan saluran dan membolehkan penskalaan kepada 3nm, 2nm dan seterusnya. Intel, TSMC dan Samsung sedang dalam proses peralihan kepada seni bina ini dengan nod Intel 18A, TSMC N2 dan Samsung SF3E mereka, antara lain.

Walau bagaimanapun, GAA dengan nanosheets juga mempunyai tarikh luput. Aspirasi besar industri logik ialah CFETdi mana transistor nyp disusun secara menegak di atas satu sama lain, supaya, pada peringkat loji, ia menempati tapak satu peranti. Ini secara praktikalnya boleh mengurangkan separuh kawasan sel kritikal tertentu dan memberikan penambahbaikan besar-besaran dalam ketumpatan dan PPA (kuasa, prestasi, kawasan).

Masalahnya ialah CFET ialah mimpi ngeri integrasi yang sebenar.Ia memerlukan kawalan bahan yang tepat dan penjajaran yang sangat tepat antara peranti yang disusun, serta koreografi proses yang sangat halus untuk mengelakkan kerosakan pada transistor di bawah semasa mengeluarkan yang di atas. Inilah sebabnya mengapa imec dan pemain lain menganggap forksheet sebagai langkah pertengahan yang munasabah: ia menggunakan semula sebahagian besar fluks GAA, menambah dinding dielektrik dan meningkatkan ketumpatan tanpa perlu beralih kepada susunan menegak penuh.

Dari perspektif temporal, IMEC meletakkan forksheet sebagai fokus utama menjelang akhir dekad ini, dengan tujuan pengeluaran sekitar tahun 2028, manakala CFET mewah lebih berkemungkinan siap pada awal pertengahan 30-an, dengan kematangan pengeluaran perindustrian sekitar tahun 2032 mengikut anggaran mereka.

Visi Samsung: forksheet mencapai 1nm

Samsung Foundry tidak lagi terhad kepada persaingan nod demi nod dengan TSMC atau mengejar garis masa Intel; Rakyat Korea jelas telah menetapkan sasaran mereka pada nod 1 nm menjelang sekitar tahun 2031, dan forksheet merupakan bahagian penting dalam strateginya. Syarikat itu ingin memberi tumpuan sepenuhnya pada ketumpatan, kecekapan dan prestasi, walaupun TSMC akan terus mendahului dari segi volum.

Dalam rancangan ini, Samsung merancang untuk menggunakan transistor dengan lebar saluran hampir 1 nmyang bersamaan dengan kira-kira lima atom. Ini bukan sekadar pengurangan tambahan daripada 2 nm, tetapi sempadan fizikal semasa sebenar berkenaan dengan kawalan saluran, pengendalian bahan dan kebolehubahan statistik peranti-ke-peranti.

Pendekatan forksheet Samsung bertujuan meminimumkan ruang antara transistor Dengan memanfaatkan batasan pengimbas litografi semasa, "dinding" penebat diperkenalkan antara peranti untuk membendung interaksi elektrik antara mereka, seterusnya meningkatkan ketumpatan per unit luas. Pemisahan fizikal yang kurang bermakna lebih banyak transistor dalam ruang yang sama, tetapi juga permintaan yang lebih besar terhadap kawalan kebocoran dan gandingan; inilah sebabnya dinding dielektrik adalah kritikal.

Sehingga kini, lompatan dari FinFET ke GAA telah pun membolehkan peningkatan ketara dalam kecekapan tenagaSaluran yang dikelilingi pada empat sisi ini mengurangkan kebocoran berbanding pintu tiga sisi FinFET. Forksheet ini menambah pengoptimuman selanjutnya dengan menangani salah satu kesesakan utama: jarak fizikal antara peranti nyp dalam sel. Untuk skala melebihi 2 nm tanpa menjejaskan penggunaan atau prestasi kuasa, penyelesaian agresif seperti ini menjadi penting.

Dalam konteks pasaran, Samsung kekal sebagai pemain utama kedua dalam operasi faundri. Dari segi volum, TSMC beroperasi dalam liga yang berbeza dengan lebih 70% bahagian pasaran global. Walaupun begitu, Korea telah memanfaatkan inovasi tepat pada masanya dengan mahir: mereka merupakan yang pertama memperkenalkan EUV dalam nod 7nm mereka dan juga yang pertama meletakkan GAA dalam pengeluaran pada 3nm. Ini tidak memberikan mereka kepimpinan pendapatan, tetapi ia telah memastikan kehadiran yang konsisten dalam perbualan teknologi.

Nod 1 nm dengan forksheet harus dilihat, buat masa ini, sebagai tanda wilayah dan cita-cita teknologi Daripada melihatnya sebagai sesuatu yang akan segera membanjiri pasaran, cabaran sebenar adalah mengubah kelebihan teori dalam ketumpatan dan PPP kepada pengeluaran sebenar dengan hasil yang munasabah dan kos yang berpatutan. Di situlah, dari segi sejarah, pemenang sebenar ditentukan: bukan pada pembentangan persidangan, tetapi di kilang.

Dinding dalam dan dinding luar: evolusi reka bentuk forksheet

Apabila imec membentangkan konsep forksheet pada tahun 2017, Seni bina asal adalah berdasarkan "dinding dalaman" Terletak di antara peranti nMOS dan pMOS dalam sel piawai, dinding penebat diperkenalkan pada awal aliran, sebelum corak get, dan sejak itu terpaksa melalui langkah pemprosesan yang tidak terkira banyaknya: pengetsaan terpilih, pemendapan dielektrik yang berbeza, rawatan haba, dan sebagainya.

Pendekatan ini menimbulkan beberapa kesukaran yang ketara. Lebar dinding itu mestilah sangat kecilpada tahap 8 hingga 10 nm, jika ketinggian sel sekitar 90 nm ingin dikekalkan. Dengan dinding yang begitu nipis yang terdedah kepada begitu banyak langkah berikutnya, sebarang sedikit pengetsaan berlebihan atau serangan kimia boleh menghakisnya secara tidak terkawal. Ini mengenakan keperluan yang sangat ketat ke atas bahan dielektrik dan toleransi proses.

Selain itu, Dalam banyak reka bentuk logik, get transistor np berkongsi sebahagian daripada surih.Dengan meletakkan penghalang tegar di antara mereka, sambungan ini menjadi rumit: sama ada pintu perlu "melompat" ke atas dinding, yang menambah kapasitans parasit yang tidak diingini, atau penyelesaian penghalaan yang lebih luar biasa diperlukan yang akhirnya menjejaskan prestasi dan kawasan.

Satu lagi titik sensitif pada helaian forksheet dinding dalaman ialah kawalan saluran. Geometri pintu gerbang dalam pelaksanaan awal hanya benar-benar merangkumi tiga sisi saluranOleh itu, kawalan elektrostatik tidak sebaik GAA buku teks. Apabila panjang saluran terus berkurangan, kehilangan kawalan relatif ini menjadi semakin bermasalah.

Berhadapan dengan batasan ini, imec telah mengambil pendekatan baharu dengan varian baharu yang dipanggil “lembaran garpu dinding luar”Dalam versi ini, dinding penebat kini terletak di pinggir sel standard, memisahkan peranti jenis yang sama milik sel bersebelahan, dan bukannya memasukkan penghalang di dalam sel itu sendiri antara nMOS dan pMOS. Ini mengubah pendekatan integrasi dengan ketara.

Apabila melakar dinding ke arah luar, Lebarnya boleh ditingkatkan kepada kira-kira 15 nm tanpa menjejaskan ketinggian keseluruhan sel.Ini membolehkan ia dibina dengan bahan dan alatan yang terkenal, seperti silikon dioksida, dan, yang paling penting, diperkenalkan kemudian dalam urutan pembuatan, sebaik sahaja langkah kritikal seperti pembentukan sumber/longkang atau pelepasan nanosheet selesai. Dengan memasuki aliran kemudian, dinding terdedah kepada proses agresif yang lebih sedikit, menjadikannya lebih mudah untuk mengekalkan integritinya.

Kelebihan kepingan forksheet dinding luar: kawalan yang lebih baik dan pembuatan yang lebih mudah

Memindahkan dinding pada forksheet dinding luar bukan sahaja meningkatkan kebolehkilangan, Ia juga memudahkan penyepaduan get transistor.Kini pintu gerbang boleh dilanjutkan secara berterusan ke atas peranti nyp tanpa perlu melintasi penghalang di tengah-tengah sel, mengurangkan kerumitan penghalaan dan mengelakkan penambahan kapasitans parasit yang tidak perlu.

Satu lagi helah menarik bagi kepingan forksheet dinding luar ialah potong dinding sedikit pada akhir prosesJika, dalam langkah terakhir, kira-kira 5 nm dinding tersebut dialih keluar, get boleh membaluti sebahagian besar saluran, memulihkan dan juga meningkatkan kawalan elektrostatik berbanding varian sebelumnya. Simulasi yang dibentangkan oleh imec menunjukkan peningkatan sekitar 25% dalam arus konduksi hasil daripada peningkatan dalam gandingan get-saluran ini.

Reka bentuk baharu ini juga menyelesaikan masalah klasik nanosheet dan generasi pertama forksheet: kesinambungan tegasan mekanikal (regangan) dalam saluranSemasa proses tersebut, topeng pelindung menutupi kawasan di mana dinding luar akan terbentuk kemudian, jadi silikon di bawah topeng kekal sebagai blok kristal berterusan. Ini membolehkan bahan sumber/saliran yang mendorong terikan—contohnya, silikon-germanium untuk pMOS—untuk menghantar terikan dengan lebih cekap ke saluran.

Dalam seni bina sebelumnya, dengan gangguan menegak dan ketakselanjaran, Usaha mekanikal itu berkurangan akibat ketidaksejajaran dan kecacatanHasilnya ialah mobiliti pembawa yang berkurangan dan, oleh itu, arus yang kurang untuk voltan yang sama. Lembaran fork dinding luar sebahagian besarnya mengelakkan masalah ini, membolehkan aplikasi terikan yang lebih seragam dan sistematik.

Simulasi dalam memori dan pengayun SRAM mengesahkan bahawa di nod A10 (sekitar 1 nm / 10 angstrom), susunan baharu ini boleh mencapai pengurangan luas sel kira-kira 22% berbanding reka bentuk A14 berasaskan nanosheet, dengan memanfaatkan pic get yang lebih ketat dan pembungkusan peranti yang serupa yang lebih padat. Dalam litar pengayun, apabila terikan penuh dikenakan, prestasi forksheet dinding luar sepadan atau melebihi reka bentuk A14 dan 2 nm yang setara; tanpa terikan, arus pengaliran menurun kira-kira 33%, menonjolkan kegenapan faktor ini.

Selain angka-angka tertentu, Kelebihan besar helaian forksheet dinding luar ialah ia mengitar semula sebahagian besar pengetahuan nanosheetIa menggunakan bahan yang biasa, peralatan sedia ada di kilang semasa dan urutan proses yang tidak memerlukan pembinaan semula seluruh kilang. Ini mengurangkan risiko, kos dan masa pematangan berbanding alternatif yang lebih mengganggu.

Cabaran dan kecacatan metrologi dalam struktur forksheet

Apabila struktur transistor menjadi lebih kecil dan rumit, Pengesanan kecacatan menjadi masalah yang semakin seriusDalam CMOS generasi akan datang, cabarannya bukan lagi sekadar "membuat transistor," tetapi dapat melihat dan mengukur dengan tepat kecacatan struktur kecil yang walau bagaimanapun mempunyai impak yang besar terhadap kelakuan elektrik.

Dalam kes FET forksheet, walaupun ketumpatan, prestasi dan kecekapan teori diperolehi.Saiz mutlak kecacatan tipikal (kekasaran garis, sisihan pic, kelengkungan, asimetri profil, dll.) tidak berkurangan dalam perkadaran yang sama seperti dimensi nominal peranti. Ini bermakna bahawa sebarang anomali kecil menduduki, secara relatif, bahagian transistor yang semakin besar, dengan kesan yang lebih ketara.

Dalam konteks ini, Teknik metrologi klasik gagal untuk mencirikan seni bina baharu ini dengan secukupnya. Dalam projek IT2 Eropah, syarikat Semilab dan pakarnya dalam elipsometri spektroskopi telah membangunkan kaedah elipsometri umum dan, khususnya, telah meneroka penggunaan Mueller Matrix Ellipsometri untuk mengesan asimetri struktur dalam tatasusunan FET forksheet.

Idea itu berlalu mensimulasikan pengukuran matriks Mueller di bawah darjah dan arah asimetri yang berbeza Dalam profil forksheet: variasi halus dalam cerun dinding, perbezaan antara cabang, selekoh kecil atau ketidaksejajaran. Daripada simulasi ini, sejauh mana tindak balas optik yang berkaitan dengan setiap jenis kecacatan boleh dibezakan antara satu sama lain diukur, dan korelasi antara parameter asimetri dikira.

Faktor kritikal dalam pengukuran optik canggih jenis ini ialah penjajaran sampel yang tepatSedikit ralat dalam kedudukan boleh menutup atau meniru asimetri tertentu, jadi sebahagian daripada kerja ini memberi tumpuan kepada pemahaman bagaimana ketidakpastian penjajaran mempengaruhi pengukuran dan mereka bentuk kaedah untuk menapis atau mengimbanginya.

Perkembangan seperti ini adalah asas bagi industri Eropah, yang bertujuan untuk memperkukuh peranannya sebagai pemain teknologi yang relevan dalam semikonduktorSelain mengeluarkan nod yang paling canggih, projek seperti ini menyediakan alat pencirian dan pengetahuan proses yang membolehkan penambahbaikan pembuatan dan meningkatkan prestasi peranti yang semakin kompleks, termasuk forksheet.

Forksheet sebagai jambatan kepada CFET dan masa depan melangkaui 2 nm

Pengeluar logik terkemuka bersetuju bahawa GAA berasaskan nanosheet tidak boleh diregangkan selama-lamanya. melangkaui beberapa generasi. Apabila nod menjadi lebih kecil—2 nm, A14, A10, dan apa sahaja yang akan datang—tuas penskalaan geometri semata-mata akan habis, dan perubahan seni bina yang lebih radikal diperlukan; tuntutan seperti pengkomputeran kuantum Mereka adalah contoh mengapa laluan kepadatan dan prestasi baharu sedang dicari.

Dalam senario itu, CFET muncul sebagai "seni bina CMOS muktamad" Dalam jangka masa panjang, menurut pakar di IMEC, menyusun transistor N dan P secara menegak secara drastik mengurangkan luas blok logik dan memori tertentu, meningkatkan ketumpatan tanpa perlu menolak pic sisi ke had yang tidak praktikal.

Tetapi, seperti yang telah dinyatakan, Integrasi CFET sangat kompleksAntara muka, ketegangan, penjajaran dan langkah proses mesti dikawal dengan tahap ketepatan yang jauh melebihi rutin semasa. Oleh itu, industri memerlukan peralihan beransur-ansur yang membolehkannya belajar, dalam pengeluaran, cara mengurus struktur hibrid dan dinding dielektrik kritikal tanpa bergantung sepenuhnya pada teknologi yang masih baru muncul.

Forksheet, dan khususnya varian dinding luar, muat betul-betul ke dalam jurang ini. Banyak pengajaran pembuatan yang dipelajari daripada menghasilkan forksheet dalam jumlah yang tinggi Ia akan boleh diguna semula untuk CFET: daripada pengendalian dinding penebat nipis, kepada kawalan terikan, kepada penyepaduan pintu kongsi dan pengurusan kecacatan dalam persekitaran kepadatan yang sangat tinggi.

IMC meletakkan forksheet dinding luar sebagai seni bina utama untuk melanjutkan era nanosheet ke nod A10Walaupun CFET sedang matang dan akan diperkenalkan secara besar-besaran pada lewat tahun 2030-an, dalam praktiknya ini bermakna bagi beberapa nod kita akan melihat seni bina wujud bersama dan bertindih: forksheet awal dalam pengeluaran, CFET dalam barisan perintis, GAA "klasik" masih dalam jumlah yang besar untuk pasaran yang tidak memerlukan teknologi terkini, dsb.

Ia juga sedang dibincangkan jenis transistor yang perlu diletakkan pada setiap sisi dinding dalam versi forksheet yang berbeza. Idea asal meletakkan nMOS di satu sisi dan pMOS di sisi yang lain, seperti dalam CMOS klasik. Walau bagaimanapun, konfigurasi sedang dipertimbangkan yang meletakkan peranti jenis yang sama di kedua-dua sisi untuk mengoptimumkan sel tertentu atau menambah baik laluan kritikal, bergantung pada keperluan reka bentuk dan jenis litar (logik, SRAM, pengayun, dll.). Sehingga hari ini, pilihan ini kekal sebagai bidang penyelidikan dan pengoptimuman yang terbuka.

Melihat ke hadapan untuk beberapa tahun akan datang, Komitmen sektor ini adalah jelas.Gunakan forksheet untuk memastikan peningkatan ketumpatan dan prestasi terus meningkat dengan pelaburan tambahan dalam proses, dan simpan lompatan paling dramatik apabila CFET benar-benar siap dan peralatan pembuatan dan metrologi dapat menyokongnya tanpa menjejaskan hasil.

Semua pergerakan yang mengelilingi helaian forksheet transistor ini menunjukkan bahawa, walaupun fizik mengenakan had yang ketat, Masih ada ruang untuk mengetatkan lagi nod di bawah 2 nmGabungan dinding dielektrik yang direka bentuk dengan baik, kawalan terikan, skema metrologi baharu dan evolusi beransur-ansur ke arah seni bina menegak membuka peluang untuk pengeluar seperti Samsung, bersama-sama pusat rujukan seperti imec, untuk terus menetapkan rentak teknologi untuk dekad akan datang, dengan syarat mereka dapat mengubah idea-idea ini menjadi barisan pengeluaran yang stabil dan menguntungkan.