- Các transistor dạng tấm chĩa tạo ra một lớp điện môi cho phép các thiết bị nyp được đặt gần nhau hơn, cải thiện mật độ, hiệu suất và hiệu quả so với GAA dạng tấm nano.

- Samsung có kế hoạch sử dụng công nghệ forksheet trong lộ trình hướng tới tiến trình 1nm, trong khi imec đang thúc đẩy các biến thể như forksheet thành ngoài để tạo điều kiện thuận lợi cho việc sản xuất đến tiến trình A10.

- Các kỹ thuật đo lường tiên tiến, bao gồm phép đo tán xạ ánh sáng bằng mảng Mueller, là chìa khóa để phát hiện các bất đối xứng và khuyết tật nghiêm trọng trong các cấu trúc dạng tấm phức tạp ngày càng gia tăng.

- Bảng phân tích cấu trúc (forksheet) được định vị như một bước trung gian chiến lược hướng tới các CFET trong tương lai, chia sẻ các quy trình và kiến thức sẽ tạo điều kiện thuận lợi cho quá trình chuyển đổi sang kiến trúc dọc xếp chồng.

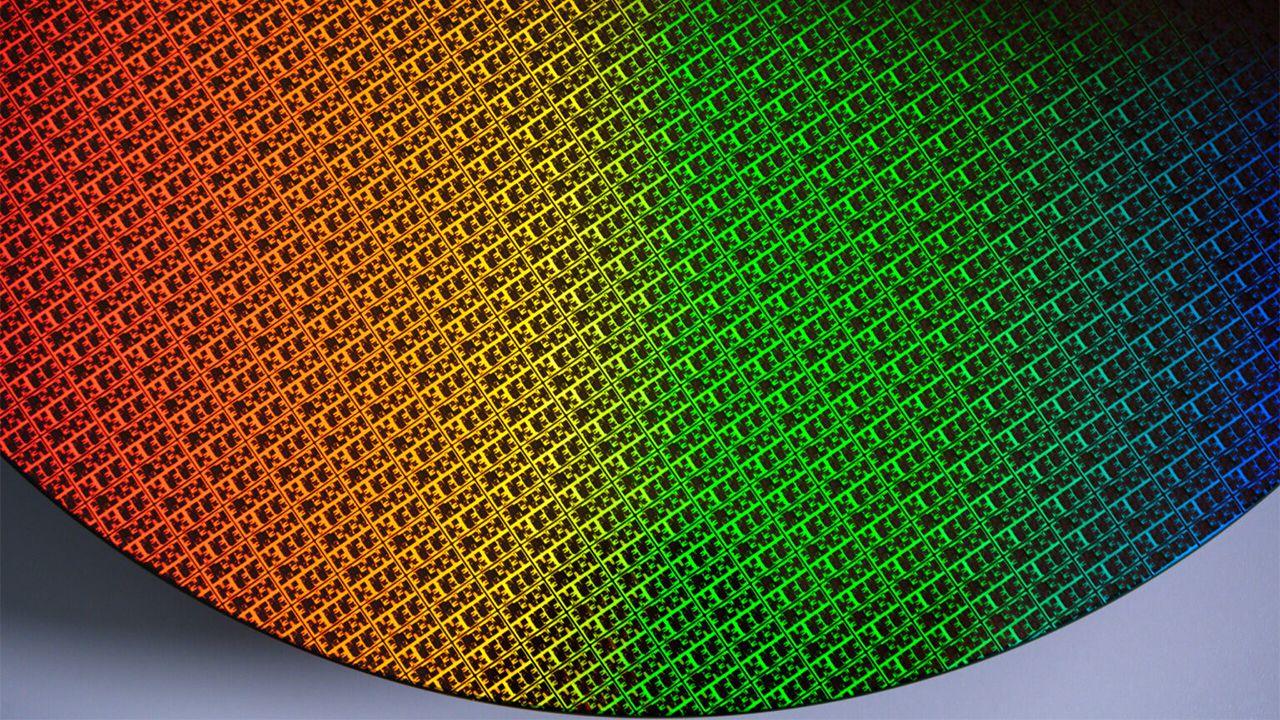

Ngành công nghiệp bán dẫn đang trải qua một thời điểm then chốt: Các bảng phân nhánh transistor đã len lỏi vào tất cả các lộ trình phát triển sản phẩm. Các nhà sản xuất hàng đầu xem đây là bước tiến lớn tiếp theo để mở rộng quy mô vượt ra ngoài các tấm nano GAA truyền thống. Và điều này không phải ngẫu nhiên: mỗi nút công nghệ mới đều đắt hơn, phức tạp hơn và dễ hỏng hơn, vì vậy bất kỳ kiến trúc nào có thể tối ưu hóa mật độ, hiệu suất và hiệu quả mà không làm tăng chi phí quá cao đều tự động trở thành một yếu tố quan trọng.

Trong bối cảnh này, Samsung, Intel, TSMC và imec đang tiến bước với tốc độ tối đa. Để xác định các thế hệ 2 nm, 1 nm và các thế hệ angstrom tiếp theo (A14, A10, A7, v.v.) sẽ như thế nào. Trong quá trình này, tấm nano hình chữ Y được định hướng là một "bước trung gian thông minh" giữa các tấm nano GAA hiện tại và các CFET (FET bổ sung) trong tương lai, sẽ xuất hiện khi việc tích hợp theo chiều dọc các thiết bị nano xếp chồng lên nhau trở thành hiện thực công nghiệp chứ không chỉ là một bài tập trong phòng thí nghiệm.

Sơ đồ mạch transistor là gì và tại sao nó lại quan trọng đến vậy?

Transistor dạng tấm chĩa là sự phát triển trực tiếp từ transistor dạng tấm nano GAA.Được thiết kế để tối đa hóa mật độ logic và SRAM mà không cần thiết kế lại hoàn toàn quy trình sản xuất, chìa khóa nằm ở việc đưa vào một lớp điện môi chiến lược cho phép các bóng bán dẫn nMOS và pMOS được đặt gần nhau hơn mà không gây ra điện dung ký sinh.

Trong các tấm nano GAA thông thường, Hạn chế không đến từ chính kênh truyền dẫn mà từ khoảng cách giữa các thiết bị bổ sung. Chúng tạo thành một cổng logic CMOS. Nếu chúng được đặt quá gần nhau, điện dung giữa các vùng N/P sẽ tăng lên đáng kể, làm giảm hiệu năng, tăng mức tiêu thụ điện năng và làm nhiễu tín hiệu. Khoảng cách tối thiểu này đang trở thành một trở ngại thực sự cho việc giảm kích thước hơn nữa của các ô tiêu chuẩn.

Imec, công ty dẫn đầu trong nghiên cứu thiết bị tiên tiến trong nhiều năm, đã bắt đầu nghiên cứu xem khả năng mở rộng quy mô của các tấm nano bắt đầu "bị phá vỡ" ở điểm nào. Kết quả của những nghiên cứu đó đã dẫn đến ý tưởng về chiếc nĩa.Thay vì để khoảng trống giữa các bóng bán dẫn bổ sung "lộ ra", một bức tường cách điện được đưa vào để phân tách vật lý các vùng thiết bị cùng loại, tùy thuộc vào biến thể.

Trong quan niệm ban đầu của nó, Tấm kẹp (forksheet) đặt một lớp điện môi bên trong giữa nMOS và pMOS. Trong cùng một ô tiêu chuẩn. Vách ngăn này cho phép hai transistor được đặt gần nhau hơn mà không làm tăng đáng kể điện dung, vì nó hoạt động như một rào cản điện giữa các cổng và vùng hoạt động. Do đó, nhà thiết kế có hai lựa chọn: giảm diện tích ô để chứa nhiều mạch logic hơn trên mỗi milimét vuông hoặc sử dụng không gian "thừa" để mở rộng các tấm nano và tăng hiệu suất.

Những con số mà ngành này xử lý không hề nhỏ: Theo kết quả mô phỏng, so với tấm nano GAA cổ điển thì tấm nano này có hiệu quả hơn.Thiết kế dạng tấm chĩa có thể đạt được hiệu suất cao hơn tới 10%, cải thiện hiệu quả năng lượng khoảng 24% và giảm diện tích tế bào gần 20%. Tất cả những điều này trong khi vẫn duy trì phần lớn các bước quy trình đã được hoàn thiện đối với các tấm nano.

Từ FinFET đến GAA và từ GAA đến forksheet: bước tiếp theo

Để hiểu được vị trí của bảng kê dụng cụ (forksheet) trong bối cảnh này, chúng ta cần nhìn lại một chút. Khi công nghệ FinFET ra mắt thị trường, chúng đã giải quyết được vấn đề điều khiển kênh. Các bóng bán dẫn phẳng gặp vấn đề khi kích thước nút thu nhỏ. "Vây" hoặc vây nâng kênh dẫn lên trong không gian 3D và cổng bao quanh ba mặt, cải thiện khả năng kiểm soát tĩnh điện và giảm rò rỉ.

Bước tiến tiếp theo là cổng bao quanh (GAA), trong đó Kênh dẫn không còn là một vây tản nhiệt mà là nhiều tấm silicon nằm ngang xếp chồng lên nhau.Được bao quanh hoàn toàn bởi cổng. Điều này giúp tăng cường khả năng kiểm soát kênh và cho phép thu nhỏ kích thước xuống 3nm, 2nm và hơn thế nữa. Intel, TSMC và Samsung đang trong quá trình chuyển đổi sang kiến trúc này với các tiến trình Intel 18A, TSMC N2 và Samsung SF3E, cùng nhiều tiến trình khác.

Tuy nhiên, ngay cả GAA có chứa các tấm nano cũng có hạn sử dụng. Khát vọng lớn lao của ngành công nghiệp logic chính là CFET.Trong đó, các bóng bán dẫn NYP được xếp chồng lên nhau theo chiều dọc, sao cho, ở cấp độ nhà máy, chúng chiếm diện tích của một thiết bị duy nhất. Điều này có thể giảm một nửa diện tích của một số tế bào quan trọng và mang lại những cải tiến đáng kể về mật độ và PPA (công suất, hiệu suất, diện tích).

Vấn đề là CFET thực sự là một cơn ác mộng về tích hợp.Việc này đòi hỏi sự kiểm soát vật liệu chính xác và sự căn chỉnh cực kỳ chuẩn xác giữa các thiết bị xếp chồng lên nhau, cũng như một quy trình phối hợp rất tinh tế để tránh làm hỏng các bóng bán dẫn bên dưới trong khi sản xuất các bóng bán dẫn phía trên. Đó là lý do tại sao imec và các nhà sản xuất khác coi tấm xếp chồng (forksheet) là một bước trung gian hợp lý: nó tái sử dụng hầu hết chất trợ hàn GAA, thêm một lớp điện môi và cải thiện mật độ mà không cần phải chuyển sang xếp chồng hoàn toàn theo chiều dọc.

Xét từ góc độ thời gian, IMEC đặt bảng thông số càng nâng làm trọng tâm chính vào cuối thập kỷ này.Với mục tiêu đưa vào sản xuất khoảng năm 2028, trong khi dòng CFET cao cấp có thể sẽ sẵn sàng vào đầu hoặc giữa những năm 30, và đạt độ chín muồi về sản xuất công nghiệp vào khoảng năm 2032 theo ước tính của họ.

Tầm nhìn của Samsung: sản xuất chip đạt công nghệ 1nm.

Samsung Foundry không còn bị giới hạn trong việc cạnh tranh từng bước một với TSMC hay đuổi theo tiến độ của Intel nữa; Rõ ràng người Hàn Quốc đang nhắm đến công nghệ sản xuất chip 1 nm. Khoảng năm 2031, bảng mạch in (forksheet) là một phần trọng tâm trong chiến lược của công ty. Công ty muốn tập trung mạnh vào mật độ, hiệu quả và hiệu năng, mặc dù TSMC vẫn sẽ dẫn đầu về sản lượng.

Trong kế hoạch này, Samsung dự định sử dụng các bóng bán dẫn có chiều rộng kênh gần 1 nm.Điều này tương đương với khoảng năm nguyên tử. Đây không chỉ là sự giảm dần kích thước từ 2 nm, mà là một bước tiến vật lý thực sự hiện nay về kiểm soát kênh dẫn, xử lý vật liệu và sự biến thiên thống kê giữa các thiết bị.

Cách tiếp cận bảng phân chia của Samsung hướng tới Giảm thiểu khoảng cách giữa các bóng bán dẫn Tận dụng những hạn chế của các máy quét quang khắc hiện tại, một "vách ngăn" cách điện được đưa vào giữa các thiết bị để hạn chế sự tương tác điện giữa chúng, từ đó tăng thêm mật độ trên mỗi đơn vị diện tích. Khoảng cách vật lý nhỏ hơn đồng nghĩa với việc có nhiều bóng bán dẫn hơn trong cùng một không gian, nhưng cũng đòi hỏi cao hơn về việc kiểm soát rò rỉ và ghép nối; đó là lý do tại sao vách ngăn điện môi lại rất quan trọng.

Cho đến nay, bước nhảy vọt từ FinFET sang GAA đã cho phép một sự cải thiện đáng kể về hiệu quả năng lượngKênh dẫn, được bao quanh bốn phía, giúp giảm rò rỉ so với cổng ba mặt của FinFET. Tấm phân nhánh (forksheet) còn tối ưu hóa hơn nữa bằng cách giải quyết một trong những nút thắt cổ chai chính: khoảng cách vật lý giữa các thiết bị nyp trong ô. Để thu nhỏ kích thước vượt quá 2 nm mà không ảnh hưởng đến mức tiêu thụ điện năng hoặc hiệu năng, những giải pháp mạnh mẽ như vậy trở nên thiết yếu.

Trong bối cảnh thị trường, Samsung vẫn là nhà sản xuất lớn thứ hai trong lĩnh vực gia công chip. Về sản lượng, TSMC hoạt động ở một đẳng cấp khác hẳn với hơn 70% thị phần toàn cầu. Mặc dù vậy, người Hàn Quốc đã khéo léo tận dụng những đổi mới kịp thời: họ là người đầu tiên giới thiệu công nghệ EUV trên tiến trình 7nm và cũng là người đầu tiên đưa công nghệ GAA vào sản xuất ở tiến trình 3nm. Điều này không mang lại cho họ vị trí dẫn đầu về doanh thu, nhưng đã đảm bảo sự hiện diện ổn định của họ trong các cuộc thảo luận về công nghệ.

Nút 1 nm với forksheet hiện tại nên được xem như là... một dấu hiệu của lãnh thổ và tham vọng công nghệ Thay vì coi đó là thứ sẽ ngay lập tức tràn ngập thị trường, thách thức thực sự nằm ở việc chuyển đổi lợi thế lý thuyết về mật độ và PPP thành sản xuất thực tế với năng suất hợp lý và chi phí phải chăng. Đó là nơi mà, theo lịch sử, những người chiến thắng thực sự được quyết định: không phải tại các buổi thuyết trình hội nghị, mà là trong nhà máy.

Thành trong và thành ngoài: sự tiến hóa của thiết kế tấm lót nĩa

Khi imec giới thiệu khái niệm bảng kê chi tiết (forksheet) vào năm 2017, Kiến trúc ban đầu dựa trên mô hình "bức tường bên trong". Nằm giữa các linh kiện nMOS và pMOS trong ô tiêu chuẩn, lớp cách điện được đưa vào từ giai đoạn đầu của quy trình, trước khi tạo mẫu cổng, và từ đó phải trải qua vô số bước xử lý: khắc chọn lọc, lắng đọng các chất điện môi khác nhau, xử lý nhiệt, v.v.

Cách tiếp cận này gặp phải một số khó khăn đáng kể. Chiều rộng của bức tường đó phải cực kỳ nhỏ.Độ dày thành tế bào vào khoảng 8 đến 10 nm, nếu muốn duy trì chiều cao tế bào khoảng 90 nm. Với thành tế bào mỏng như vậy phải trải qua nhiều bước xử lý tiếp theo, bất kỳ sự ăn mòn quá mức hoặc tấn công hóa học nào cũng có thể làm mòn nó một cách không kiểm soát. Điều này đặt ra những yêu cầu rất khắt khe đối với vật liệu điện môi và dung sai của quy trình.

Bên cạnh đó, Trong nhiều thiết kế mạch logic, các cổng của transistor np chia sẻ một phần đường dẫn tín hiệu.Bằng cách đặt một rào cản cứng giữa chúng, kết nối này trở nên phức tạp: hoặc cửa phải "vượt" qua bức tường, điều này làm tăng điện dung ký sinh không mong muốn, hoặc cần các giải pháp định tuyến bất thường hơn, dẫn đến ảnh hưởng đến hiệu năng và diện tích.

Một điểm nhạy cảm khác của tấm đỡ vách trong là việc kiểm soát kênh dẫn. Hình dạng hình học của cổng trong thiết kế ban đầu chỉ thực sự bao trùm ba cạnh của kênh.Do đó, khả năng điều khiển tĩnh điện không tốt bằng GAA trong sách giáo khoa. Khi chiều dài kênh tiếp tục giảm, sự mất kiểm soát tương đối này càng trở nên nghiêm trọng hơn.

Trước những hạn chế này, imec đã áp dụng một phương pháp mới với một biến thể mới có tên gọi là... “bảng hướng dẫn sử dụng tường ngoài”Trong phiên bản này, vách cách điện giờ đây nằm ở rìa của ô tiêu chuẩn, ngăn cách các thiết bị cùng loại thuộc các ô liền kề, thay vì chèn rào cản bên trong chính ô đó giữa nMOS và pMOS. Điều này làm thay đổi đáng kể phương pháp tích hợp.

Khi phác thảo bức tường hướng ra phía ngoài, Chiều rộng của nó có thể được tăng lên khoảng 15 nm mà không ảnh hưởng đến chiều cao tổng thể của tế bào.Điều này cho phép nó được chế tạo bằng các vật liệu và công cụ quen thuộc, chẳng hạn như silicon dioxide, và trên hết, được đưa vào quy trình sản xuất muộn hơn, sau khi các bước quan trọng như tạo nguồn/thoát hoặc giải phóng tấm nano đã hoàn tất. Bằng cách tham gia vào dòng chảy muộn hơn, thành ống sẽ tiếp xúc với ít quá trình khắc nghiệt hơn, giúp dễ dàng duy trì tính toàn vẹn của nó.

Ưu điểm của tấm càng nâng thành ngoài: kiểm soát tốt hơn và sản xuất dễ dàng hơn

Việc di dời vách trên tấm càng nâng ngoài không chỉ cải thiện khả năng sản xuất, Điều này cũng giúp đơn giản hóa việc tích hợp cổng transistor.Giờ đây, cổng có thể được mở rộng liên tục trên các thiết bị nyp mà không cần phải vượt qua rào cản ở giữa ô, giảm độ phức tạp của việc định tuyến và tránh thêm điện dung ký sinh không cần thiết.

Một thủ thuật thú vị khác của tấm ván lót tường ngoài là... Cắt bớt phần tường một chút ở cuối quá trình.Nếu ở các bước cuối cùng, khoảng 5 nm của bức tường đó được loại bỏ, cổng có thể bao quanh một phần lớn hơn của kênh, khôi phục và thậm chí cải thiện khả năng điều khiển tĩnh điện so với biến thể trước đó. Các mô phỏng do imec trình bày cho thấy dòng điện dẫn tăng khoảng 25% nhờ sự cải thiện này trong liên kết cổng-kênh.

Thiết kế mới này cũng giải quyết một vấn đề kinh điển của các tấm nano và thế hệ tấm hình chữ Y đầu tiên: sự liên tục của ứng suất cơ học (biến dạng) trong kênhTrong quá trình này, một lớp mặt nạ bảo vệ bao phủ khu vực nơi bức tường ngoài sẽ hình thành sau này, do đó silicon bên dưới lớp mặt nạ vẫn là một khối tinh thể liên tục. Điều này cho phép các vật liệu nguồn/thoát gây ra ứng suất—ví dụ, silicon-germanium cho pMOS—truyền ứng suất đến kênh hiệu quả hơn.

Trong các kiến trúc trước đây, với những sự gián đoạn và ngắt quãng theo chiều dọc, Nỗ lực cơ học đó bị suy giảm do sự sai lệch và các khiếm khuyết.Kết quả là độ linh động của các hạt tải điện giảm, và do đó, dòng điện cũng giảm ở cùng một điện áp. Tấm đỡ hình chữ Y ở thành ngoài phần lớn tránh được những vấn đề này, cho phép phân bổ ứng suất đồng đều và có hệ thống hơn.

Các mô phỏng trong bộ nhớ SRAM và bộ dao động xác nhận rằng tại nút A10 (khoảng 1 nm / 10 angstrom), cấu trúc mới này có thể giảm diện tích tế bào khoảng 22% so với các thiết kế A14 dựa trên tấm nano, tận dụng lợi thế của khoảng cách cổng hẹp hơn và mật độ đóng gói dày đặc hơn của các thiết bị tương tự. Trong các mạch dao động, khi áp dụng lực căng tối đa, hiệu suất của tấm nano ở thành ngoài tương đương hoặc vượt trội so với các thiết kế A14 và 2 nm tương đương; nếu không có lực căng, dòng điện dẫn giảm khoảng 33%, cho thấy tầm quan trọng của yếu tố này.

Ngoài những con số cụ thể, Ưu điểm vượt trội của tấm nano dạng càng cua ở thành ngoài là nó tái sử dụng phần lớn bí quyết công nghệ của tấm nano.Phương pháp này sử dụng các vật liệu quen thuộc, thiết bị hiện có trong các nhà máy hiện tại và các quy trình sản xuất không yêu cầu xây dựng lại toàn bộ nhà máy. Điều này giúp giảm thiểu rủi ro, chi phí và thời gian hoàn thiện so với các phương án thay thế mang tính đột phá hơn.

Những thách thức và sai sót trong đo lường cấu trúc tấm kim loại dạng càng nâng

Khi cấu trúc transistor trở nên nhỏ hơn và phức tạp hơn, Việc phát hiện lỗi đang trở thành một vấn đề nan giải ngày càng lớn.Trong công nghệ CMOS thế hệ tiếp theo, thách thức không còn chỉ là "chế tạo transistor", mà là khả năng quan sát và đo lường chính xác những khuyết tật cấu trúc nhỏ nhất, vốn lại có tác động rất lớn đến tính chất điện của transistor.

Trong trường hợp FET dạng tấm chĩa, mặc dù Mật độ, hiệu suất và hiệu quả lý thuyết được cải thiện.Kích thước tuyệt đối của các khuyết tật điển hình (độ nhám đường kẻ, độ lệch bước, độ cong, độ bất đối xứng biên dạng, v.v.) không giảm theo cùng tỷ lệ với kích thước danh nghĩa của thiết bị. Điều này có nghĩa là bất kỳ sự bất thường nhỏ nào cũng chiếm một phần ngày càng lớn hơn trong transistor, với những ảnh hưởng rõ rệt hơn.

Trong ngữ cảnh này, Các kỹ thuật đo lường cổ điển không đáp ứng được yêu cầu. Để mô tả đầy đủ các kiến trúc mới này. Trong khuôn khổ dự án IT2 của châu Âu, công ty Semilab và các chuyên gia về phép đo quang phổ elip đã phát triển các phương pháp đo elip tổng quát và đặc biệt, đã nghiên cứu việc sử dụng phép đo elip ma trận Mueller để phát hiện sự bất đối xứng cấu trúc trong các mảng FET dạng chĩa ba.

Ý tưởng đi qua Mô phỏng các phép đo ma trận Mueller dưới các mức độ và hướng bất đối xứng khác nhau. Trong mặt cắt hình nĩa: những biến đổi nhỏ về độ dốc thành, sự khác biệt giữa các nhánh, các khúc uốn nhỏ hoặc sự lệch hướng. Từ những mô phỏng này, mức độ phân biệt được các phản ứng quang học liên quan đến từng loại khuyết tật được định lượng và mối tương quan giữa các tham số bất đối xứng được tính toán.

Một yếu tố quan trọng trong loại phép đo quang học tiên tiến này là sự căn chỉnh chính xác của mẫuMột sai sót nhỏ trong định vị có thể che giấu hoặc bắt chước một số bất đối xứng nhất định, vì vậy một phần công việc tập trung vào việc hiểu cách độ không chắc chắn trong căn chỉnh ảnh hưởng đến các phép đo và thiết kế các phương pháp để lọc hoặc bù trừ cho nó.

Những phát triển này có vai trò nền tảng đối với ngành công nghiệp châu Âu. nhằm mục đích củng cố vai trò của mình như một nhà cung cấp công nghệ quan trọng trong lĩnh vực bán dẫn.Ngoài việc sản xuất các nút công nghệ tiên tiến nhất, các dự án như thế này còn cung cấp các công cụ phân tích đặc tính và kiến thức về quy trình, cho phép tinh chỉnh quá trình sản xuất và cải thiện hiệu suất của các thiết bị ngày càng phức tạp, bao gồm cả các tấm đỡ phân phối điện.

Forksheet đóng vai trò là cầu nối đến CFET và tương lai vượt ra ngoài công nghệ 2 nm.

Các nhà sản xuất mạch logic hàng đầu đều đồng ý rằng GAA dựa trên tấm nano không thể kéo giãn vô hạn. vượt qua một vài thế hệ. Khi các nút ngày càng nhỏ hơn—2 nm, A14, A10, và bất cứ thứ gì tiếp theo—các đòn bẩy của việc thu nhỏ hình học thuần túy đã cạn kiệt, và cần có những thay đổi kiến trúc triệt để hơn; những yêu cầu như... điện toán lượng tử Chúng là một ví dụ cho thấy lý do tại sao người ta đang tìm kiếm những hướng đi mới về mật độ và hiệu suất.

Trong trường hợp đó, CFET được xem là "kiến trúc CMOS tối ưu". Theo các chuyên gia tại IMEC, về lâu dài, việc xếp chồng các transistor N và P theo chiều dọc sẽ làm giảm đáng kể diện tích của một số khối logic và bộ nhớ nhất định, tăng mật độ mà không cần phải đẩy khoảng cách ngang đến mức không thực tế.

Nhưng, như đã đề cập trước đó, Việc tích hợp CFET vô cùng phức tạp.Các giao diện, lực căng, sự căn chỉnh và các bước quy trình phải được kiểm soát với độ chính xác vượt xa những gì hiện đang được thực hiện thường xuyên. Do đó, ngành công nghiệp cần một quá trình chuyển đổi dần dần cho phép họ học hỏi, trong quá trình sản xuất, cách quản lý các cấu trúc lai và các vách điện môi quan trọng mà không hoàn toàn dựa vào một công nghệ vẫn còn đang phát triển.

Các tấm càng nâng, đặc biệt là biến thể thành ngoài, hoàn toàn phù hợp với khoảng trống này. Nhiều bài học kinh nghiệm về sản xuất đã được rút ra từ việc sản xuất tấm càng nâng với số lượng lớn. Chúng sẽ có thể tái sử dụng cho CFET: từ việc xử lý các vách cách điện mỏng, đến kiểm soát biến dạng, đến việc tích hợp các cổng dùng chung và quản lý các khuyết tật trong môi trường mật độ rất cao.

IMC đặt tấm càng cua tường ngoài như Kiến trúc then chốt để mở rộng kỷ nguyên tấm nano đến nút A10Mặc dù CFET đang trong giai đoạn hoàn thiện và sẽ được ứng dụng rộng rãi vào những năm 2030, trên thực tế điều này có nghĩa là đối với một số thế hệ chip, chúng ta sẽ thấy các kiến trúc cùng tồn tại và chồng chéo nhau: các bảng phân nhánh ban đầu được sản xuất hàng loạt, CFET trong các dây chuyền thí điểm, GAA "cổ điển" vẫn được sản xuất với số lượng lớn cho các thị trường không cần công nghệ mới nhất, v.v.

Vấn đề này cũng đang được thảo luận. Nên đặt loại bóng bán dẫn nào ở mỗi bên của bức tường? Trong các phiên bản bảng mạch in khác nhau, ý tưởng ban đầu là đặt nMOS ở một bên và pMOS ở bên kia, giống như trong CMOS cổ điển. Tuy nhiên, các cấu hình đang được xem xét để đặt các thiết bị cùng loại ở cả hai phía nhằm tối ưu hóa một số ô nhất định hoặc cải thiện các đường dẫn quan trọng, tùy thuộc vào nhu cầu thiết kế và loại mạch (logic, SRAM, bộ dao động, v.v.). Cho đến nay, lựa chọn này vẫn là một lĩnh vực nghiên cứu và tối ưu hóa mở.

Nhìn về phía trước trong vài năm tới, Cam kết của ngành này rất rõ ràng.Sử dụng bảng phân nhánh để duy trì sự gia tăng mật độ và hiệu năng bằng cách đầu tư từng bước vào quy trình, và dành bước nhảy vọt ngoạn mục nhất cho đến khi CFET thực sự sẵn sàng và các công cụ sản xuất và đo lường có thể hỗ trợ mà không làm giảm năng suất.

Tất cả những chuyển động xung quanh các bảng mạch in transistor cho thấy rằng, mặc dù vật lý đặt ra những giới hạn nhất định, Vẫn còn dư địa để tiếp tục thu nhỏ các nút xuống dưới 2 nm.Sự kết hợp giữa các vách ngăn cách điện được thiết kế tốt, kiểm soát biến dạng, các phương pháp đo lường mới và sự phát triển dần dần hướng tới kiến trúc thẳng đứng mở ra cơ hội cho các nhà sản xuất như Samsung, cùng với các trung tâm tham khảo như imec, tiếp tục dẫn đầu về công nghệ trong thập kỷ tới, với điều kiện họ có thể biến những ý tưởng này thành các dây chuyền sản xuất ổn định và có lợi nhuận.